Application Note

March 1997

AN120.1

# Introduction

An important requirement in many systems is the ability to off-load numeric data processing. In an 80C286 system, this can be accomplished with an 80287 numeric co-processor. However, as processor speeds increase, it may become necessary to interface a high speed 80C286 processor with a lower speed 80287. This Document will briefly describe the interface between a 16MHz 80C286 (80C286-16) and a 10MHz 80287 (80287-10).

Interfacing the 80C286 with an 80287 can be broken down into three main areas:

- Bus control lines and data lines which coordinate and implement the flow of data between the two processors (i.e. the data lines, chip select lines, and read/write lines).

- (2) The clock line(s), which drive the two processors.

- (3) The four status lines through which the 80C286 and 80287 directly communicate status information to one another - comprised of the BUSY, ERROR, Peripheral Request (PEREQ), and Peripheral Acknowledge (PEACK) lines.

#### **Bus Control Lines**

The various bus control and data lines in most systems would be coordinated by either a bus controller (such as the 82C288), or a bus controller subsection of an 80C286 oriented chip set. All requisite bus control timing between a 16MHz 80C286, and a 10MHz 80287 would then be handled by these devices (typically with one wait-state inserted to allow for the slower 80287-10).

#### **Clock Lines**

A system using a 16MHz 80C286 with a 10MHz 80287 requires separate clock lines for the two processors. The 32MHz system clock used by the 80C286-16 is too fast for the 80287  $\pm$ 10, necessitating a dedicated clock driver for the 80287. This clock driver should supply a 10MHz clock to the

80287 with a 1/3 duty cycle to allow the 80287-10 to run at it's full 10MHz capability. One solution for providing this clock is the 82C84A-1, which meets this specification with either a 30MHz crystal at it's crystal inputs, or a 30MHz external frequency input to it's EFI pin. In either case, a 10MHz 1/3 duty cycle clock is output to the 80287. Note that when using a dedicated clock driver such as this, the CKM pin of the 80287 must be pulled up.

### Status Lines

The 80C286 and 80287 communicate status information with one another through four signals; the BUSY line, the ERROR line, the peripheral request line (PEREQ), and the PEACK line.

The BUSY and ERROR lines can be connected from the 80287 to a 80C286-oriented chipset, or from the 80287 directly to a 80C286. In the case of the chipset interface, the signal timing between the 80287 and 80C286 is coordinated by the chipset. In the case of the direct 80287 to 80C286 interface, the signal timing is handled by the 80C286, and, since the signal flow direction is from the 80287 to the 80C286 (i.e. from the slower device to the faster device), no additional hardware is required to achieve proper timing.

The peripheral request (PEREQ) line should be connected directly from the 80287 to the 80C286, and again, since the signal flow direction is from the 80287 to the 80C286, no additional hardware is required.

The peripheral acknowledge ( $\overrightarrow{PEACK}$ ) line is normally connected directly from the 80C286 to the 80287. In this case the signal flow direction is from the 80C286 to the 80287 (i.e. faster device to slower device), and the  $\overrightarrow{PEACK}$  active time is not guaranteed to meet the requirements of the slower 80287-10. Worst case timing for the 80C286-16 reveals that  $\overrightarrow{PEACK}$  output could be as short as 45.5ns (i.e.  $\overrightarrow{PEACK}$  (min) = 45.5ns). The 80287-10 input requirement is  $\overrightarrow{PEACK}$  (min) = 60ns. (min) = 45.5ns). The 80287-10 input require

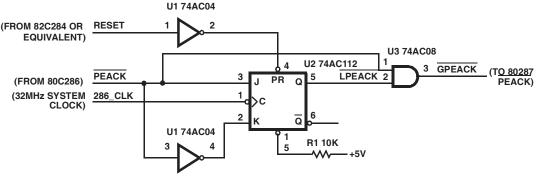

FIGURE 1. PEACK STRETCH CIRCUIT

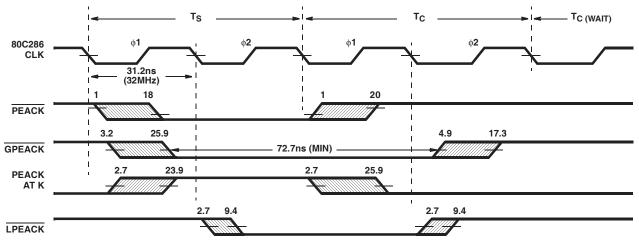

The proper PEACK timing can be achieved using the circuit shown in Figure 1 comprised of a 74AC04, 74AC08, and a 74AC112. Referring to the timing diagram shown in Figure 2, it can be seen that this circuit effectively "stretches" the 80C286's PEACK output (in the form of GPEACK) to 72.7ns, which satisfies the 80287-10 requirement.

The operation of the circuit shown in Figure 1 is as follows:

- (1) The RESET signal (which is also applied to the 80C286) is used to initialize the 'AC112 to a known inactive state (Q = 1).

- (2) When the 80C286 asserts the PEACK signal, the gated version of this signal (GPEACK) is asserted with minimal delay (7.9ns through the 'AC08).

- (3) On the falling edge of the 80C286 CLK at the beginning of Phase 2 of the T<sub>S</sub> cycle, the low state of <u>PEACK</u> is clocked into the 'AC112. This effectively holds <u>GPEACK</u> <u>low for</u> an additional clock cycle longer than standard <u>PEACK</u> timing.

- (4) On the falling edge of the 80C286 CLK at the beginning of phase 2 of the first T<sub>C</sub> cycle, the high state of <u>PEACK</u> is clocked into the 'AC112, which then causes <u>GPEACK</u> to go inactive.

The net effect of this circuit operation is to extend the 80C286's Peripheral Acknowledge signal to the 80287-10 sufficiently to meet it's requirements.

FIGURE 2. PEACK CYCLE TIMING

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# Sales Office Headquarters

## NORTH AMERICA

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 EUROPE Intersil Europe Sarl Ave. C - F Ramuz 43 CH-1009 Pully Switzerland TEL: +41 21 7293637 FAX: +41 21 7293684 ASIA Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433

2